# 基于安全控制边界单元的 IP 核测试封装方法

俞 洋,向 刚,乔立岩

(哈尔滨工业大学自动化测试与控制系,黑龙江哈尔滨 150001)

摘 要: 为了解决测试信息传递的问题,IEEE 组织推出了 IEEE1500 IP (Intellectual Property)核测试封装标准以标准化 IP 核测试接口.然而该标准给出的典型测试封装存在由测试数据扫描移入造成的不安全隐患.本文提出了一种基于安全控制边界单元的 IP 核测试封装方法.这种方法的核心思想是在典型的测试封装边界单元的基础上添加一个 CMOS(Complementary Metal Oxide Semiconductor)传输门,有效消除了测试过程中扫描移位对被测 IP 核电路的影响.实验结果表明,这种基于安全控制边界单元的测试封装能够在完成测试任务的同时,有效降低 IP 核输入端口的测试数据数据跳变次数,使 IP 核处于安全状态,还可以降低扫描移位过程中产生的动态测试功耗.

关键词: 系统芯片; IEEE 1500 标准; 测试封装; 传输门

中图分类号: TP391.76 文献标识码: A 文章编号: 0372-2112 (2011) 3A-099-05

# Secure Test Wrapper Design for Embedded IP Cores

YU Yang, XIANG Gang, QIAO Li-yan

(Department of Automatic Test and Control, Harbin Institute of Technology, Harbin, Heilongjiang 150001, China)

Abstract: The IEEE 1500 standard was proposed to standardize the IP (Intellectual Property) core test interface to transfer test information. But the typical IEEE 1500-compliant test wrapper would lead IP cores into an insecure status during scan shifting. This paper presented a secure test wrapper design for embedded IP cores, which only inserted a CMOS (Complementary Metal Oxide Semiconductor) transmission gate to the test wrapper cell to eliminate the precarious effect to IP cores. Experiments show that the proposed test wrapper not only takes less area overhead and time delay, but also can test the data path and reduce the data transitions at the input port of IP cores, thus decreases the dynamic test power during scan shifting.

Key words: system-on-a-chip; IEEE 1500 standard; test wrapper; transmission gate

# 1 引言

随着集成电路深亚微米制造技术和设计技术的迅速发展,集成电路的规模越来越大,使得原来要由多个芯片才可以实现的复杂系统被集成在单个芯片上成为可能.在这种背景下,基于 IP 核复用的系统芯片(System-On-a-Chip, SOC)应运而生.

当 IP 核被集成到 SOC 后,其输入输出端口也就嵌入到 SOC 中,这样使得原本可测的端口就失去了原有的可控性和可观测性,不能保证已经经过设计验证的 IP 核在嵌入到 SOC 后不会出现问题.如何通过 SOC 系统级的输入输出端口实现对各个 IP 核的测试访问就是 SOC 测试所必须解决的核心问题[1].目前国际上常采用的方法是在 IP 核上加载一个测试封装<sup>[2,3]</sup>,该测试封装不仅能实现 SOC 中各个 IP 核之间的测试隔离,而且能提供 IP 核测试数据的快速传输通道. Marinissen 等人提

出的 Test Shell<sup>[4]</sup>以及 Vanma 等人提出的 Test Collar<sup>[5]</sup>都是典型的测试封装结构. IEEE 组织也为此制定了 IP 核测试标准——IEEE 1500<sup>[6,7]</sup>,该标准规定了一种可扩展的测试封装结构,旨在标准化 IP 核测试接口,使得 IP 核的测试变得方便高效,它主要由以下几部分组成:

- (1)串行访问接口 WSP(Wrapper Serial Port)和并行访问接口 WPP(Wrapper Parallel Port),是测试激励输入和测试响应输出的接口;

- (2) 旁路寄存器 WBY(Wrapper Bypass Register),该寄存器在测试封装串行接口的输入输出之间提供了一条数据传输的快速通道;

- (3)边界寄存器 WBR(Wrapper Boundary Register)由 外围的边界单元组成,用于实现 IP 核的可控性和可观 测性;

- (4)控制接口 WIP(Wrapper Instruction Port)和指令寄存器 WIR(Wrapper Instruction Register), WIP 由 8 个控制

信号组成,这些信号控制 WIR 的操作.

文献[8]给出了测试封装各个部分的设计过程和方法.在测试封装的各个组成部分中,边界寄存器 WBR 由测试封装边界单元构成,担负着测试数据的移入和移出任务.文献[7]给出了 IEEE 1500 标准规定的典型的测试封装边界单元,该单元是面积最小的扫描单元,但是由该单元组成的 WBR 在扫描操作时会使 IP 核处于不安全状态,并且带来较高的动态功耗.为此,文献[9]和[10]提出了一种基于多路选择器的测试封装边界单元结构,虽然解决了安全移位问题,但会带来较大的功能信号延时和面积开销;文献[11]详细分析了各种端口的情况,并给出了最小的测试封装边界单元库.

本文首先对 IEEE 1500 标准给出的典型测试封装 边界单元和安全控制测试封装边界单元进行分析,指 出各自的优势和存在的问题;然后具体描述了本文提出的基于传输门的安全控制边界单元结构,这种测试 封装边界单元结构简单,能够弥补已有各种测试封装 边界单元的不足,同时保持他们的优点;以这种扫描单元为基础,设计了 IP核测试封装,最后通过实验证明本 文所提出的 IP核测试封装方法在时延,面积开销以及减少动态测试功耗上的优越性.

### 2 测试封装边界单元工作原理

为了实现对 IP 核的测试,测试封装必须支持以下四种工作模式:(1)功能模式,核和其他模块正常工作,即测试封装是透明的;(2)扫描测试模式,在这种模式下,芯片通过测试访问机制将测试激励传送到 IP 核的输入端口;测试封装检测 IP 核的输出响应,并将其传送到测试宿;(3)复位模式,在这种模式下,芯片上的其他核处于扫描测试模式,该核自身则处于测试复位状态,不影响其他 IP 核的测试;(4)互连测试,在这种模式下,各 IP 核处于测试复位模式,而芯片通过 TAM 和各 IP 核的测试封装向核与核之间的互连逻辑施加测试激励并观测响应.

# 3 测试封装边界单元

#### 3.1 典型测试封装边界单元

测试封装边界单元能实现测试激励的施加和测试响应的捕获,从而实现对 IP 核的可控制性和可观测性. IEEE 1500 给出了一种典型的边界单元的实现方式<sup>[7]</sup>, 如图 1 所示.

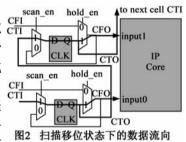

该边界单元中 CFI 为功能数据输入端口,CFO 为功能数据输出端口,CTI 为扫描数据输入端口,CTO 为扫描数据输入端口,hold\_

en 为测试允许控制信号, scan\_ en 为扫描允许信号, CLK 为时钟信号. 这种结构能够实现功能、移位、捕获和保持/施加操作, 不同操作的控制信号值列于表 1 中.

表 1 不同操作的控制信号值

| scan_en | hold_en |

|---------|---------|

| X       | 0       |

| 1       | X       |

| 0       | 0       |

| 0       | 1       |

|         |         |

在扫描移位的过程中,数据流是由 CTI 到 CTO.尽管从理论上,hold\_en信号可以取值为 0,测试数据移位对被测 IP的功能引脚没有影响.但在实际的测试封装设计过程中,hold\_en信号由测试指令译码产生.根据

IEEE1500 的推荐电路,在测试移位和激励施 CFIT加时,hold\_ en 信号始终保持在高电平,造成了 CFO与 CTO 的连通,CFI工这样在扫描移位过程中,无序的扫描数据将通过 CFO 端口使 IP 核

处于某种不安全状态,图 2 给出了移位状态下数据的流向.另外,由于 CFO 的连续跳变,使 IP 核内部状态也不断地变化,从而产生巨大的额外动态功耗.

### 3.2 安全控制测试封装边界单元

为了解决 IEEE 1500 典型的测试壳单元的不足,一 种改进方法是在 CFO 之后增加阻隔逻辑,以实现安全 控制.文献[12]利用或非门实现安全控制.文献[9]和文 献[10]则在 CFO 后增加一个多路选择器,从而改进了 IEEE 1500 测试壳单元结构中存在的无序的扫描数据带 来的不安全性和高动态功耗,这种结构与 IEEE 1500 典 型测试封装边界单元的区别在于增加了一个控制信号 safe\_en 和安全值 safe,在扫描移位过程中通过 safe\_en 实现 CFO 和 CTO 的隔离,并且 CFO 输出安全值 safe,从 而使测试封装扫描链与 IP 核内部逻辑的隔离,实现测 试数据的安全移位操作,减少移位过程中的动态功耗. 但是该结构由于增加了一个多路选择器,使得功能路 径时延增加,这会影响功能状态下功能输入端口与 IP 核内部逻辑间的数据通信速度,甚至降低芯片的工作 频率,使测试时间延长,增加测试成本.另外,增加的多 路选择器也会导致额外的面积开销.

# 4 改进的测试封装边界单元结构

从上面的分析可知,已有文献提出的测试封装边界单元都有其不足.为了减少时延和面积开销,本文采用一种互补金属氧化物半导体(CMOS, Complementary

Metal Oxide Semiconductor)传输门<sup>[13]</sup>的方法来实现测试封装边界单元的安全控制.

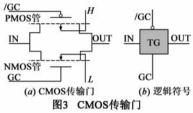

#### 4.1 CMOS 传输门

CMOS 传输门电路和符号如下图 3 所示. CMOS 传输门由一对互补 NMOS 和 PMOS 管并联而成. 两个管的源极相连作为输入端 IN,漏极相连作为输出端 OUT,两管的栅极作为控制端,分别作用一对互为反向的控制电压 GC 和/GC,可以控制传输门的导通或关闭. P 管和 N 管的衬底分别接电源 VDD 和地端 GND.

传输门是一种可控的开关电路,它接近于一个理想的电子开关,开关接通时自身的电阻很小,相当于短路,而开关断开时其电阻很大,相当于开路.传输门的开启和关闭是由互补脉冲控制的,当 GC = 0,/GC = 1时,传输门关闭,输出端 OUT 为高阻态(Z态);当 GC = 1,/GC = 0时,传输门开启,OUT = IN.传输门的状态如表 2 所示.

表 2 传输门的状态

| sign | nals | input | output |

|------|------|-------|--------|

| GC   | /GC  | IN    | OUT    |

| 1    | 0    | 0     | 0      |

| 1    |      | 1     | 1      |

| 0    | 1    | 0     | Z      |

|      | 1    | 1     | Z      |

由于 MOS 管的结构对称,源极和漏极可以互换,电流可以从两个方向流通,传输门的输入端和输出端可以互换使用,可以任意把其中一个作输端,另一个作输出端,所以又称它为双向开关.

传输门关闭时,输出 OUT 呈高阻态,也即浮空状态,这同样会引起 IP 核内部的逻辑混乱,使 IP 核处于不安全状态.所以必须使传输门关闭时,输出能够稳定处于某一确定值.本文提出在传输门输出端增加控制单元以使其输出稳定.

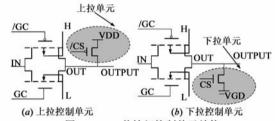

#### 4.2 控制单元原理

控制单元的结构如下图 4 所示. 一种控制单元是在传输门的输出端 OUT 增加一个 PMOS 管,构成上拉控制单元,见图 4(a),通过控制信号 CS 控制该 CMOS 管.另一种控制单元则是通过增加一个 NMOS 管,构成下拉单元以实现控制功能,见图 4(b).

图 4 中上拉控制单元的控制机制如下:

(1)当传输门处于关闭状态,OUT端处于高阻态时,

将 CS 赋值为逻辑 0,使 PMOS 管导通,将输出端 OUTPUT 上拉为逻辑 1.此时 OUT = OUTPUT = 1.

(2)当传输门处于导通状态时,控制 CS 为逻辑 1, PMOS 管截止,此时 IN = OUT = OUTPUT.

下拉控制单元的控制机制以此类推:

- (1)当传输门处于关闭状态,OUT端处于高阻态时,将CS赋值为逻辑1,使NMOS管导通,将输出端OUT-PUT下拉为逻辑0,此时OUT=OUTPUT=0.

- (2)当传输门处于导通状态时,控制 CS 为逻辑 0, NMOS 管截止,此时 IN = OUT = OUTPUT.

图4 COMS传输门控制单元结构

#### 4.3 基于传输门的测试封装边界单元

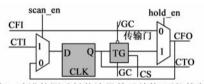

本文提出的测试封装边界单元是在典型测试封装 边界单元的 D 触发器和选择器之间增加一个带下拉控 制单元的 CMOS 传输门,其结构如图 5 所示.

图5 改进的测试封装边界单元结构(下拉控制)

改进的测试封装边界单元能够实现功能、移位、捕获和保持/施加操作.不同操作下控制信号的值列于表 3 中.

表 3 改进的测试封装边界单元的控制信号值

| 操作 | Scan_en | hold_en | GC | /GC | CS |

|----|---------|---------|----|-----|----|

| 功能 | x       | 0       | X  | x   | x  |

| 移位 | 1       | 1       | 0  | 1   | 1  |

| 捕获 | 0       | 0       | x  | X   | x  |

| 施加 | 0       | 1       | 1  | 0   | 0  |

尽管改进的测试封装单元增加了三个控制信号,但仔细分析上表可以看出,信号 GC = /Scan\_en,信号/GC = CS = Scan\_en. 因此,新增的控制信号可以在内部通过 Scan\_en信号得到,/GC和 CS可以直接从 Scan\_en得到,GC可以由 Scan\_en取非得到.因此,改进的测试封装单元不需要额外的译码电路产生控制信号.

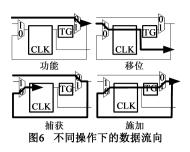

图 6 表示在不同的操作下,测试数据的流向图,图中用黑粗线表示.

改进测试封装边界单元在测试激励的施加过程时,需要传输门开启,以便触发器通过传输门向 CFO 传输数据;而在测试数据的移位过程中时,传输门则处于

关闭状态,实现 CFO 和CTO 的阻隔.通过下拉单元控制,使 CFO 输出固定的低电平,这样就可以使 IP 核处于安全状态,大大减小了被测IP 核内部逻辑在扫描移位时的频繁跳变产

生的无用动态功耗.另一方面,由于传输门没有加在功能路径上,因此与安全控制测试封装边界单元相比,减少了功能路径上的延迟.

### 5 实验结果分析

### 5.1 测试封装边界单元性能评价

衡量测试封装边界单元性能优劣可从面积开销,信号延迟和功耗等几方面考虑.在目前已经提出的方法中,使用多路选择器或者或非门(NOR)实现安全控制是较好的方法之一,NOR由4个晶体管组成,多路选择器则更复杂,而本文提出的传输门仅由3个晶体管构成.由于晶体管数量与面积,功耗基本成正比,因此本文提出的改进的测试封装边界单元构成的测试封装将具有更少的面积和功耗开销.

表 4 给出了多路选择器、或非门和传输门在面积、时延和功耗上的比较,从表中可以看出,传输门结构无论在面积,时延开销还是功耗上都具有优越性.

| 表 4 | 选择器. | 一。北京 | 与传输i | 门的比较 |

|-----|------|------|------|------|

|     |      |      |      |      |

|         | MUX   | 或非门   | 传输门   |

|---------|-------|-------|-------|

| 面积(um²) | 0.32  | 0.28  | 0.18  |

| 时延(ps)  | 91.28 | 41.65 | 22.47 |

| 功耗(uw)  | 20.73 | 12.34 | 7.39  |

#### 5.2 基于安全控制边界单元的测试封装性能评价

本文提出的基于传输门的安全控制边界单元解决了扫描移入过程对被测 IP的影响,我们将本文提出的测试封装边界单元应用于 IP核测试封装的设计.

我们知道,扫描移位过程中,测试封装扫描链上将产生大量的电平翻转.文献[7]中传统的测试封装边界单元由于 CTO 端口和 CFO 端口的连通,测试封装扫描链上数据的变化将直接影响被测 IP输入端口上数据的变化,使得被测 IP处于不安全状态,甚至还会在其内部产生很大的额外功耗.因此,本文采用被测 IP输入端口上数据的翻转次数来衡量被测 IP核的安全程度和额外功耗情况.

实验在基准电路集 ISCAS'89<sup>[14]</sup>上进行,采用 Mintest 工具<sup>[15]</sup>产生的测试向量.首先来衡量应用典型的测试封装<sup>[7]</sup>、基于多路选择器的测试封装<sup>[10]</sup>、基于或非门测试封装<sup>[12]</sup>和本文方法后,被测 IP 输入的安全控

制程度.实验结果如表5中所示.表5中.第1列是采用的基准电路,第2列是测试向量的大小,第3列到第6列分别是采用典型方法、多路选择器方法、或非门方法和本文方法后,加载测试向量时IP核输入端口状态的翻转次数.从表中可以看出,多路选择器方法、或非门方法和本文方法都能非常有效地消除扫描数据对IP核功能电路的影响.

表 5 四种方法在 IP 核输入端跳变次数的比较

| 基准     | 测试数据   | 典型方法[7] | MUX <sup>[10]</sup> | 或非门[12] | 本文方法 |  |  |

|--------|--------|---------|---------------------|---------|------|--|--|

| 电路     | (bit)  | 跳变次数    | 跳变次数                | 跳变次数    | 跳变次数 |  |  |

| S298   | 425    | 151     | 0                   | 0       | 0    |  |  |

| S382   | 672    | 209     | 0                   | 0       | 0    |  |  |

| S5378  | 23754  | 3993    | 0                   | 0       | 0    |  |  |

| S13207 | 165200 | 8342    | 0                   | 0       | 0    |  |  |

| S38584 | 199104 | 25104   | 0                   | 0       | 0    |  |  |

表6给出了典型方法、多路选择器方法、或非门方法和本文方法在硬件开销上的比较.表中第1列表示所采用的电路;第2列是采用典型的测试壳单元进行封装后,各电路的大小;第3列表示采用多路选择器方法后在典型方法基础上增加的晶体管数量和增加的面积开销比例;第4列表示采用或非门方法后在典型方法基础上增加的晶体管数量和增加的面积开销比例;第5列表示采用本文方法后在典型方法基础上增加的晶体管数量和增加的面积开销比例.从表中可以看出,本文方法在所增加的硬件开销上要明显小于前两种方法.

表 6 四种方法在硬件开销上的比较

| 农 6 首件为法任政计划销工的比较 |                         |                     |                   |                  |                   |                  |                   |

|-------------------|-------------------------|---------------------|-------------------|------------------|-------------------|------------------|-------------------|

|                   | 典型<br>方法 <sup>[7]</sup> | MUX <sup>[10]</sup> |                   | 或非门[12]          |                   | 本文方法             |                   |

| 基准电路              |                         | 增加的<br>晶体管<br>数量    | 额外面<br>积开销<br>(%) | 增加的<br>晶体管<br>数量 | 额外面<br>积开销<br>(%) | 増加的<br>晶体管<br>数量 | 额外面<br>积开销<br>(%) |

| S27               | 876                     | 63                  | 7.20              | 36               | 4.11              | 27               | 3.08              |

| S382              | 1129                    | 63                  | 5.58              | 36               | 3.19              | 27               | 2.39              |

| S5378             | 12721                   | 588                 | 4.62              | 336              | 2.64              | 252              | 1.98              |

| S13207            | 37492                   | 1064                | 2.84              | 608              | 1.62              | 456              | 1.21              |

| S38584            | 84086                   | 2030                | 2.41              | 1160             | 1.38              | 870              | 1.04              |

虽然相对于 IEEE 1500 给出的典型的测试封装边界单元,本文提出的测试封装边界单元由于增加了传输门,在面积上会有所增加,但相比已经提出的安全控制测试封装,本文方法面积增加最小.另外,本文方法解决了测试封装扫描链在扫描移位过程中的安全移位问题,使动态功耗减少.因此综合来看,本文提出基于安全控制边界单元的测试封装具有更优越的性能.

# 6 结论

IP 核测试是近几年 SOC 测试方面的热点问题之一.为 IP 核添加符合 IEEE 1500 标准的测试封装是解决 IP 核测试复用的关键.本文提出的基于安全控制边界单元的测试封装在 IEEE 1500 给出的典型的测试封装

上进行改进,在测试封装边界单元上增加一个晶体管级的传输门,不仅实现了功能路径的测试,而且解决了测试封装扫描链在扫描移位过程中的安全移位问题.实验数据表明,本文所提出的测试封装能够完全解决扫描移位过程中扫描数据对 IP 核功能电路的影响,并且相比与 IEEE1500 标准推荐的测试封装结构,其平均硬件开销仅增加了 2%左右,相比已有方法具有比较明显的优势.因此,本文方法具有一定的实用价值.

#### 参考文献

- [1] Mullane Brendan, Higgins Michael, Namee Ciaran Mac. An optimal IEEE 1500 core wrapper design for improved test access and reduced test time[A]. IET Irish Signals and Systems Conference[C]. Galway, Ireland: Institution of Engineering and Technology, 2008.204 209.

- [2] Benso Alfredo, DI Carlo stefano, et al. IEEE standard 1500 compliance verification for embedded cores[J]. IEEE Transactions on Very Large Scale Integration (VLSI) System, 2008, 16(4):397 407.

- [3] Higgins M, Macnamee C, Mullane B. Design and implementation challenges for adoption of the IEEE 1500 standard[J]. IET Computers & Digital Techniques, 2010, 4(1):38 49.

- [4] Marinissen Erik Jan, Arendsen Robert, et al. A structured and scalable mechanism for test access to embedded reusable cores [A]. Proceedings of the 1998 IEEE International Test Conference[C]. Piscataway: Institute of Electrical and Electronics Engineers Inc, 1998.284 – 302.

- [5] Varma Prab, Bhatia Sandeep. A structured test re-use methodology for core-based system chips [A]. Proceedings of the 1998 IEEE International Test Conference [C]. Piscataway: Institute of Electrical and Electronics Engineers Inc, 1998. 294 302.

- [6] IEEE Std 1500-2005. IEEE 1500 Standard for Embedded Core Test[S].

- [7] Silva Francisco da, Mclaurin Teresa, Waayers Tom. The Core Test Wrapper Handbook; Rationale and Application of IEEE Std.1500[S].2005.147 – 155.

- [8] 乔立岩,向刚,俞洋.基于 IEEE 1500 标准的 IP 核测试壳设计[J].电子测量技术.2010,33(7):88 91.

Qiao Li-yan, Xiang gang, Yu Yang. Design of IP core test wrapper based on IEEE 1500 standard[J]. Electronic Measurement Technology,2010,33(7):88 91. (in Chinese)

- [9] 丁颖,殷燕芬.基于 IP 核测试复用的内核测试壳单元的设计研究[A].中国通信集成电路技术与应用研讨会论

- 文集[C].北京:《中国集成电路》杂志社,2005.185-190.

- [10] Chal Crou. Design-for-test for Digital IC's and Embedded Core Systems[M]. Upper Saddle River: Prentice Hall PTR, 1999, 175 240.

- [11] Marinissen Erik Jan, Goel Sandeep Kumar, Lousberg Maurice. Wrapper design for embedded core[A]. Proceedings of International Test Conference[C]. Piscataway: Institute of Electrical and Electronics Engineers Inc, 2000.911 915.

- [ 12 ] Gerstendrfer Stefan, Wunderlich Hans-Joachim. Minimized power consumption for scan-based BIST[J]. Journal of Electronic Testing: Theory and Applications, 2000, 16(3): 203 212.

- [13] Bhunia Swarup, Mahmoodi Hamid, Ggosh Debjyoti. Low-power scan design using first-level supply gating [J]. IEEE Transactions on Very Large Scale Integration Systems, 2005, 13(3):384 395.

- [14] Brglez Franc, Bryan David, Kozminski Krzysztof. Combinational profiles of sequential benchmark circuits [A]. Proceedings of IEEE International Symposium on Circuits and Systems [C]. Piscataway: Institute of Electrical and Electronics Engineers Inc, 1989. 1924 1934.

- [15] Hhmzaoglu Illker, Patel Janak H. Test set compaction algorithms for combinational circuits [J]. IEEE Transactions on Computer-Aided Design of Intergrated Circuits and Systems, 2000, 19(8):957 963

#### 作者简介

**俞 洋** 女,博士,1979年11月生于黑龙江大庆市,哈尔滨工业大学自动化测试与控制系讲师.主要研究方向为SoC测试与故障诊断技术

E-mail: yuyanghit53@163.com

**向 刚** 男,1985年12月出生于湖北咸宁. 2009年毕业于哈尔滨工业大学自动化测试与控制系.现为哈工大自动化测试与控制研究所硕士研究生,研究方向为 SOC 测试.

E-mail: hit-xianggang@163.com