# 40Gbps 甚短距离并行光传输技术与实验系统

## 胡庆生,许 多,苗 澎

(东南大学射频与光电集成电路研究所,江苏南京 210096)

摘 要: 介绍了40Gbps 甚短距离(VSR)并行光传输系统的实现和测试.用两片 Altera Stratix II GX FPGA 分别实现发送/接收转换芯片,通过对 FPGA 内嵌的吉比特收发器的合理配置,以及在去斜移电路中采用滑动窗口生成器和共用窗口比较器的方法节省了硬件资源;基于异或定位原理,采用二分查找法大大提高了帧同步电路的速度.自制的12通道垂直腔面发射激光器(VCSEL)的工作速率达到了 12×3.318Gbps.利用 Agilent 81250 误码仪,通过并行光发射/接收模块和7米长的12芯多模带状光纤,成功实现了 SDH STM256/OC768 的点到点测试,连续两小时的测试结果表明,系统误码率小于10<sup>-12</sup>,满足设计要求.

关键词: 甚短距离;光传输;垂直腔面发射激光器;去斜移;帧同步;误码率

中图分类号: TN913 文献标识码: A 文章编号: 0372-2112 (2011) 05-1174-04

## 40Gbps Very Short Reach Parallel Optical Transmission and System

HU Qing-sheng, XU Duo, MIAO Peng

(Institute of RF- and OE-ICs, Southeast University, Nanjing, Jiangsu 210096, China)

Abstract: The design and measurement of 40Gbps Very Short Reach (VSR) parallel optical transmission system are presented. The transmitter and receiver are implemented using Altera Stratix II GX PFGA which has embedded high-speed transceiver. By configuring the high-speed transceiver correctly, using window generator and sharing the window comparator within the deskew module, the hardware area is reduced greatly. Binary search is also employed in the frame synchronization module to raise the circuit speed. Additionally, a 12 × 3.318Gbps VCSEL transmitter is researched and works correctly. At last, the VSR5 point-to-point measurement is undertaken by connecting the receiver and transmitter via a 7-meter 400MHz·km 62.5µm multi-mode fiber ribbon and Agilent tester. Under the continuous test of 2 hours, a system bit error rate(BER) of lower than 10<sup>-12</sup> is obtained.

**Key words:** very short reach; optical transmission; vertical cavity surface emitting laser(VCSEL); de-skew; frame synchronization; bit error rate(BER)

## 1 引言

甚短距离(VSR, Very Short Reach)并行光传输是一种采用低成本光收发模块并行垂直腔面发射激光器(VCSEL, Vertical Cavity Surface Emitting Laser)及并行光互连技术,在不降低系统总吞吐量的前提下,降低每根光纤的传输速率,从而实现的一种简单、廉价和可靠的光传输方式,主要应用于建筑物、机房内的短距离、低成本设备的互连[1].该技术已经成为通信领域的热门技术,国际上也不断有相关产品推出,如 CISCO 公司的基于VSR4 的 10Gbps 速率的产品[2].国内也研制出了 10Gbps速率的 VCSEL发射阵列[3-5],并且推出了符合 VSR4 标准的并行光传输系统[6,7].

VSR5 是光互联论坛针对 40Gbps 甚短距离光互连制定的接口标准<sup>[8,9]</sup>,基于这一标准,近年来国内外对 40Gbps 的 VSR5 开展了研究,并取得了一定的进展.但

这些研究主要集中在并行光收发模块方面<sup>[10,11]</sup>,在 VSR5 系统方面的研究结果尚不多见.本文主要介绍自行研制的 40Gbps 的 VSR5 实验系统,重点介绍了转换芯片的设计及整个 VSR5 点到点实验系统的测试.

## 2 VSR5 实验系统的设计

#### 2.1 VSR5 实验系统结构

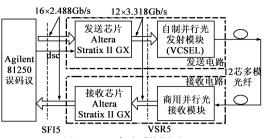

图 1 所示为 VSR5 实验系统框图. 收发电路各采用一片 Altera 公司 65nm 工艺的 Stratix II GX EP2SGX130 作为发送和接收芯片,另外,还各有一块  $12 \times 3.318$ Gbps的并行光发射和接收模块,发送电路与接收电路通过 7 米长的 12 芯 400MHz·km 62.5 $\mu$ m 多模带状光纤相连. 收发芯片系统侧的接口为 SFI5 接口,其定义为  $16 \times 2.488$ Gbps的数据外加一路同样速率的去斜移通道 (DSC, DeSkew Channel);用户侧的接口则为 VSR5,其数据率为  $12 \times 3.318$ Gbps,收发芯片的主要功能就是实现

SFI5 与 VSR5 之间的转换.

图1 VSR5实验系统框图

### 2.2 转换芯片的设计与实现

图 2 为转换芯片结构框图.在发送方向,由 SFI5 输入的 OC768 帧经过 Altera FPGA 内嵌的吉比特高速收发器 ALT2GXB(后面简称 GXB)<sup>[12]</sup>,进行时钟恢复、串并转换,得到 16 路 2.488Gbps 的数据以及 DSC 数据,与此同时,GXB恢复出 155.52MHz 的时钟作为芯片内部的系统时钟.之后,这 16 路数据被送到去斜移电路以便去除16 路数据之间的斜移量,然后,通道重排电路将对齐后的数据转换成 16 个 OC-48 帧格式. OC768 帧同步电路实现帧头的查找和帧对齐,随后,16:12 映射模块将OC768 帧分配到 12 个通道上,最后,数据经过 GXB 的32:1 并串转换后输出到光发送模块.接收方向的功能与发送方向类似.

本系统实现的关键是速率为 40Gbps 的发送/接收芯片的设计,尤其是在要求误码率低于 10<sup>-12</sup>的条件下,下面主要介绍转换芯片中关键模块的设计与实现.

#### 2.2.1 高速收发器 GXB

本系统采用的 EP2SGX130 含有 20 个高速 GXB,每个 GXB 包括锁相环、串并转换、字节对齐和相位补偿等模块.其支持的单方向最大传输速率达 6.375Gbps,并且接收和发送可以采用不同的速率,符合 SFI5 和 VSR5 两种接口的速率要求.由于发送和接收的速率可以不同,GXB的时钟管理比较复杂,有一系列的时钟管脚.

以发送芯片为例, 收、发数据的速率分别为2.488Gbps和3.318Gbps,需要为GXB提供2种频率的参考时钟:155.52MHz和103.68MHz.具体做法是, 板上晶

振产生的 155.52MHz 时钟通过芯片的输入管脚进入增强型 锁相环 (EPLL),为接收 GXB (GXB\_RX)提供 155.52MHz 的参考时钟,该时钟可以通过芯片内部的全局时钟线引入到 GXB\_RX 中.而发送 GXB(GXB\_TX)的参考时钟必须由芯片的外部管脚引入,因此,先要将 GXB\_RX 恢复出的 155.52MHz 的时钟通过时钟引脚输出,然后通过 PCB上的走线输入另一 EPLL,分频后得到 103.68MHz 的时钟输出到片外,再经过外部的时钟管理模块输出给 GXB\_TX 的专用参考时钟引脚.使用时钟管理模块的目的是增加时钟线的驱动能力.

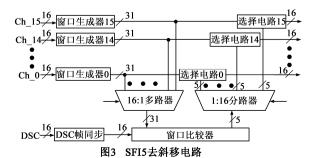

#### 2.2.2 发送芯片的去斜移和通道重排

发送芯片收到 SFI5 侧的 16 路数据后,首先要通过去斜移电路将 16 路数据信号重新对齐,以消除传输过程引入的斜移量,图 3 为其实现框图.首先,滑动窗口生成器得到 31 比特宽的"窗口";然后,窗口比较器将"窗口"中的数据与 DSC 同步后的数据进行比较,一旦检测到了 DSC 中对该路复制字节的位置并确定了数据的斜移量,就将结果输出给选择电路;最后,选择电路根据接收到的斜移量信息,从 31 比特的数据中选择 16 比特去斜移后的数据输出.本电路的特点是一个窗口比较器与多路器、分路器配合工作,实现 16 个通道的轮流去斜移,提高了工作速度,节省了资源.

窗口比较器从输入的并行数据流中检测出可能存在的某特定码组,并输出其位置.窗口比较器由选择电路,16个比较器和编码电路组成,输入的并行数据流(d1)和特定码组(d2)位宽均为16比特,窗口的宽度设为31比特,由当前输入的数据和上一时钟输入数据的低15比特组成.16个比较器并行工作,检例特定码组 d2[15:0]是否存在于窗口中,若当前窗口不包含该码组,则比较器的输出 C[15:0]各位全为零;一旦检测到特定码组的存在,则将码组位置编码输出并给出相应的指示信号.

DSC 帧同步电路通过检测 DSC 的帧定界符 *A*1*A*1(F6F6H)和 *A*2*A*2(2828H)找到每一帧的起始位置,并将结果提供给各路数据作为去斜移的参考.

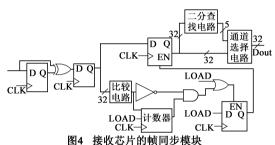

2.2.3 接收芯片的帧同步和通道对齐

帧同步模块的功能就是搜索出帧同步码,确定帧

头所在的位置,接收芯片与发送芯片均有帧同步模块,两者实现的原理相似,只是前者实现的是 12 路数据的帧同步,后者是 16 路数据的帧同步.接收芯片的帧同步模块如图 4 所示,它由异或逻辑、二分查找电路和通道选择电路等组成.其中,异或逻辑由一个与数据等宽的异或门,一个判断是否为"0"的比较电路以及一个计数器等组成,负责定位 A1A2 交界处所在的帧.二分查找电路则采用二分查找法快速找到并指示 A1A2 的交界在 32 位数据中的位置.将接收的前一个周期的数据与后一个周期的数据进行异或,一旦检测到异或结果不是全"0",找到第一个为"1"的位置,就能快速找到 A1A2 的交界处,实现帧同步.

帧同步模块之后是通道对齐模块,主要由两部分构成,一部分为12路信号的缓冲区;另一部分进行偏移量的计算并生成读指针从缓冲区中读出12路信号.以读指针生成电路为例,首先将12路信号分成两组进行比较,并根据比较结果启动计数器.偏移量处理单元计算每组中其它通道相对于基准通道的偏移量.读指针计算单元根据两个偏移量处理单元的结果,找出最迟到达的通道,并计算出所有其它通道相对于该通道的偏移.最后,将最迟到达通道的读指针设为0,计算出其它通道的读指针,并将12路信号分别从缓冲区中读出.

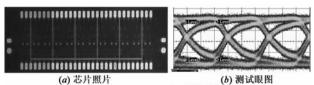

### 2.3 并行光发射模块

本实验系统中,并行光发射模块 12 × 3.318Gbps VCSEL为自制模块,其中,VCSEL阵列与驱动电路的集成采用金丝压焊工艺,各通道相互独立,支持热插拔.图 5 所示为采用 Jazz 0.35μm SiGe BiCMOS 工艺制作的12×3.318Gbps 激光驱动器芯片照片及电源电压为3.3V 时的测试眼图<sup>[14]</sup>.

图5 12×3.318Gbps激光驱动器

#### 2.4 收发电路板

VSR5 实验系统采用收、发两块电路板实现,两块板的一侧通过 SMA 头与误码测试仪 Agilent 81250 相连,另一侧通过 7米的 12 芯光纤相连.每块板各包含一片 20

个高速通道的 Altera EP2SGX130GF1508 芯片,12 路并行 光发射/接收模块,以及配置电路,时钟模块和调试接 口等,各由一块电源板供电.

## 3 VSR5 点到点实验系统的测试

误码率的测试采用 Agilent 81250 误码测试仪实现,它由包含 17 个 2.7Gbps 数据模块的码型发生器和 16 个数据分析模块的误码分析器组成.测试时,码型发生器发送的数据由文件从外部导入,其数据为 2<sup>23</sup> - 1 的伪随机码(PRBS),速率为 2.488Gbps.经过发送芯片输出后,光发射模块以 12 × 3.318Gb/s 的信号发出,通过 7米光纤和光接收模块后到达接收端,经接收芯片处理后将 16 路 2.488Gbps 信号发送给误码分析器计算误码,从而实现了 40Gbps 的点到点测试.连续二小时的测试无误码,经计算,系统误码率小于 10<sup>-12</sup>.

### 4 结语

本文设计实现了 40Gbps 的 VSR5 实验系统.采用两片 Altera 带高速收发器的 FPGA 实现了收、发转换芯片的全部功能,自行研制了 12 通道 VCSEL 光发射模块,并成功应用于系统中.采用 Agilent 误码仪,通过 7 米 12 芯 400MHz km 多模带状光纤将发送和接收电路相连,进行了点到的点的测试,结果表明误码率低于 10<sup>-12</sup>.

#### 参考文献

- [1] 陈弘达,左超.甚短距离光传输技术[M].北京:科学出版 社,2005.

- [2] Cisco White Paper. Very Short Reach OC-192/STM-64 Interface: Optimizing for Network Intra-POP Interconnections with Very Short Reach Interface [Z]. San Jose: Cisco Systems, 2000.

- [3] 黄 ■, 王志功, 李连鸣, 等. 0.25 μm CMOS 工艺实现的 3.125 Gbit/s×12 通道 VCSEL 驱动器阵列[J]. 电子学报, 2004, 32(2):323 325.

Huang Ting, et al. Monolithically integrated 0.25 μm CMOS VCSEL driver array for 3.125 Gbs×12 channels parallel optical interface[J]. Acta Electronical Sinica, 2004, 32(2):323 325. (in Chinese)

- [4] 王晓明,王志功,苗澎,等.10Gbit/s 甚短距离并行光传输模块研究[J].电路与系统学报,2004,9(4):1-4. Wang Xiaoming, et al. Research on 10 Gbit/s very short reach parallel optical transmission module [J]. Journal of Circuits and Systems,2004,9(4):1-4.(in Chinese)

- [5] 申荣铉,陈弘达,毛陆虹,等,10Gb/s 甚短距离(VSR)并行 光传输系统[J].高技术通讯,2004,13(4):105-110.

- [6] 苗澎, 王志功, 李彧. 10Gbit/s 甚短距离并行光传输模块与实验系统[J]. 电子学报, 2007, 35(2): 304 306.

- Miao Peng, et al. 10Gbit/s very short reach parallel optical transmission module and system [J]. Acta Electronical Sinica, 2007,35(2):304-306. (in Chinese)

- [7] 陈雄斌,刘丰满,刘博,等.基于 STM-64 的甚短距离并行 光传输系统[J].光电子.激光,2008,19(8):1050 – 1053. Chen Xiongbin, et al. Very short reach parallel optical transmission system based on STM-64[J]. Journal of Optoelectronics Laser,2008,19(8):1050 – 1053. (in Chinese)

- [8] OIF-SFI5-01.02 Serdes framer interface level 5 (SFI-5): implementation agreement for 40Gb/s interface for physical layer devices[S]. Optical Internetworking Forum, 2002.

- [9] OIF-VSR5-01.0 Very short reach interface level 5 (VSR-5): SONET/SDH OC-768 interface for very short reach (VSR) applications [S]. Optical Internetworking Forum, 2002.

- [10] Opnext Corporation. 40G VSR Transceivers [Z]. http://www.opnext.com;Opnext Corporation,2008.

- [11] Liu Fengman, Tang Jun, Chen Xiongbin, et al. 40Gbps Parallel Optical Module Based On an Advanced Structure of Optical Coupling [A]. Asia-Pacific Optical Communications [C]. Hangzhou, 2008.

- [12] Stratix II GX Transceiver User Guide [Z]. Altera Corporation. February 2007.

- [13] 任滨,王志功,苗澎,等.40Gbps 甚短距离光传输系统的 去斜移设计[J].光通信技术,2008,32(9):1-4.

- [14] 解峰.12 路并行 40Gb/s 0.35 μm SiGe BiCMOS 高速激光 驱动器设计与实现[D]. 南京: 东南大学硕士学位论文, 2009.

#### 作者简介

胡庆生 女,1964年出生,现为东南大学信息科学与工程学院教授,博士生导师,研究领域包括通信系统设计、高速超大规模集成电路设计.

E-mail: qshu@seu.edu.cn

**许 多** 男,1985 年出生,硕士,研究方向 为通信集成电路设计,现在华为技术有限公司工 作.